Los superlativos abundan en Cerebras, la sigilosa compañía de chips de silicio de próxima generación que busca hacer de la capacitación un modelo de aprendizaje profundo tan rápido como comprar pasta de dientes en Amazon. Lanzado después de casi tres años de desarrollo silencioso, Cerebras presentó su nuevo chip hoy, y es una maravilla. El “motor de escala Wafer” tiene 1,2 billones de transistores (el mayor número de la historia), 46,225 milímetros cuadrados (el más grande) e incluye 18 gigabytes de memoria en el chip (la mayor cantidad de cualquier chip en el mercado actual) y 400,000 núcleos de procesamiento ( adivina el superlativo).

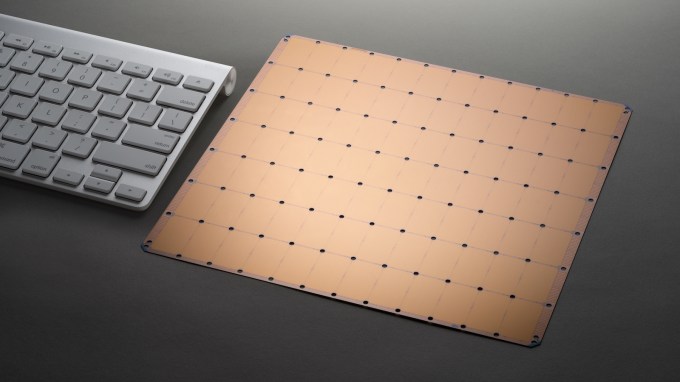

El Wafer Scale Engine de Cerebras es más grande que un teclado Mac típico (a través de Cerebras Systems)

Ha tenido un gran impacto aquí en la Universidad de Stanford en la conferencia Hot Chips, una de las grandes reuniones de la industria del silicio para la presentación de productos y hojas de ruta, con varios niveles de oohs y aahs entre los asistentes. Puede leer más sobre el chip de Tiernan Ray en Fortune y leer el libro blanco de Cerebras.

Sin embargo, aparte de los superlativos, los desafíos técnicos que Cerebras tuvo que superar para alcanzar este hito, creo que es la historia más interesante aquí. Esta tarde me senté con el fundador y CEO Andrew Feldman para hablar sobre lo que sus 173 ingenieros han estado construyendo silenciosamente en los últimos años aquí con $ 112 millones en fondos de capital de riesgo de Benchmark y otros.

Ir a lo grande no significa más que desafíos

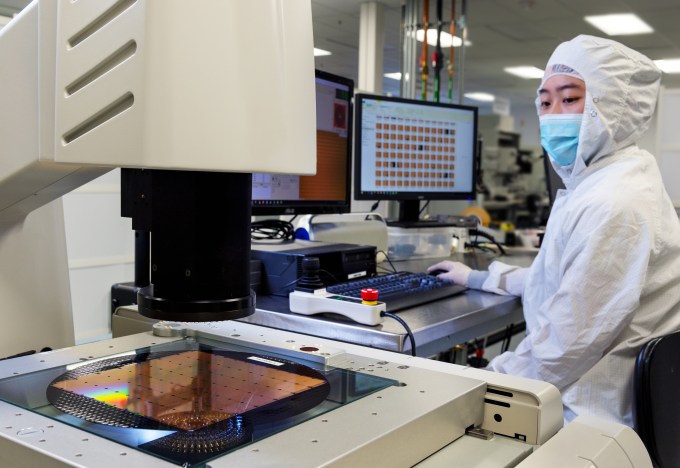

Primero, un resumen rápido sobre cómo se hacen los chips que alimentan sus teléfonos y computadoras. Fab como TSMC toman obleas de silicio de tamaño estándar y las dividen en chips individuales usando luz para grabar los transistores en el chip. Las obleas son círculos y las fichas son cuadrados, por lo que hay algo de geometría básica involucrada en la subdivisión de ese círculo en una matriz clara de chips individuales.

Un gran desafío en este proceso de litografía es que los errores pueden colarse en el proceso de fabricación, lo que requiere pruebas exhaustivas para verificar la calidad y obligar a las fábricas a tirar los chips de bajo rendimiento. Cuanto más pequeño y compacto sea el chip, es menos probable que un chip individual deje de funcionar y mayor será el rendimiento del fab. Mayor rendimiento es igual a mayores ganancias.

Cerebras descarta la idea de grabar un grupo de chips individuales en una sola oblea en lugar de usar toda la oblea como un chip gigantesco. Eso permite que todos esos núcleos individuales se conecten entre sí directamente, acelerando enormemente los circuitos de retroalimentación críticos utilizados en los algoritmos de aprendizaje profundo, pero tiene el costo de enormes desafíos de fabricación y diseño para crear y administrar estos chips.

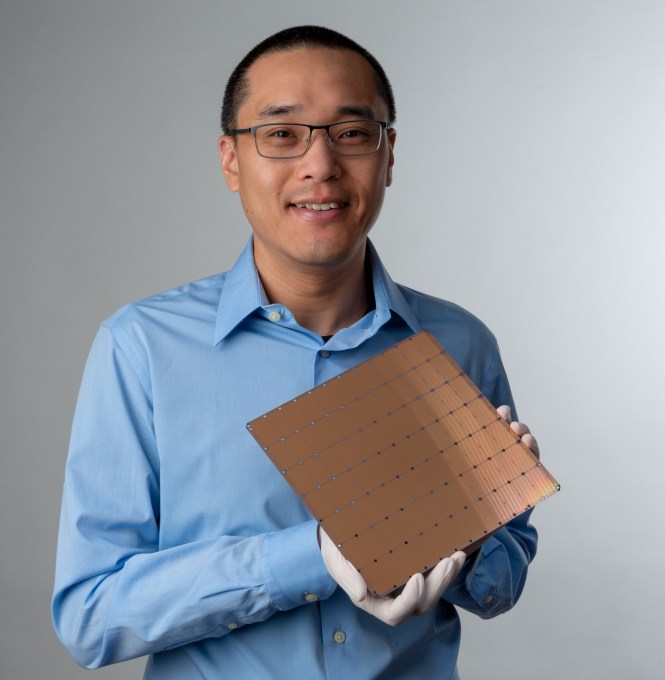

La arquitectura técnica y el diseño de Cerebras fueron dirigidos por el cofundador Sean Lie. Feldman y Lie trabajaron juntos en una startup anterior llamada SeaMicro, que se vendió a AMD en 2012 por $ 334 millones. (Vía Sistemas Cerebras)

Según Feldman, el primer desafío con el que se encontró el equipo fue manejar la comunicación a través de las “líneas de escritura”. Si bien el chip Cerebras abarca una oblea completa, el equipo de litografía de hoy en día todavía tiene que actuar como si hubiera chips individuales grabados en la oblea de silicio. Por lo tanto, la empresa tuvo que inventar nuevas técnicas para permitir que cada uno de esos chips individuales se comunicara entre sí a través de toda la oblea. Trabajando con TSMC, no solo inventaron nuevos canales de comunicación, sino que también tuvieron que escribir un nuevo software para manejar chips con trillones más transistores.

El segundo desafío fue el rendimiento. Con un chip que cubre una oblea de silicio completa, una sola imperfección en el grabado de esa oblea podría hacer que todo el chip no funcione. Este ha sido el bloqueo durante décadas en toda la tecnología de obleas: debido a las leyes de la física, es esencialmente imposible grabar repetidamente un billón de transistores con una precisión perfecta.

Cerebras abordó el problema utilizando redundancia agregando núcleos adicionales en todo el chip que se utilizarían como respaldo en caso de que apareciera un error en la vecindad de ese núcleo en la oblea. “Tienes que mantener solo el 1%, el 1.5% de estos tipos a un lado”, me explicó Feldman. Dejar núcleos adicionales permite que el chip se auto-cure esencialmente, enrutando el error de litografía y haciendo viable un chip de silicio de oblea completo.

Entrar en territorio desconocido en el diseño de chips

Esos dos primeros desafíos, comunicarse a través de las líneas de escritura entre chips y rendimiento de manejo, han desconcertado a los diseñadores de chips que han estudiado chips de obleas enteras durante décadas. Pero eran problemas conocidos, y Feldman dijo que en realidad eran más fáciles de resolver que lo esperado al volver a abordarlos utilizando herramientas modernas.

Sin embargo, compara el desafío con escalar el Monte Everest. “Es como si el primer grupo de chicos no pudo escalar el Monte Everest, dijeron:” Mierda, esa primera parte es realmente difícil “. Y luego apareció el siguiente grupo y dijo:” Esa mierda no fue nada. Esos últimos cien metros, eso es un problema “.

Y, de hecho, los desafíos más difíciles de acuerdo con Feldman para Cerebras fueron los siguientes tres, ya que ningún otro diseñador de chips había superado la comunicación de la línea de escritura y los desafíos de rendimiento para descubrir qué sucedió después.

El tercer desafío que Cerebras enfrentó fue manejar la expansión térmica. Los chips se calientan mucho en funcionamiento, pero diferentes materiales se expanden a diferentes velocidades. Eso significa que los conectores que unen un chip a su placa base también necesitan expandirse térmicamente a la misma velocidad para que no se formen grietas entre los dos.

Feldman dijo que “¿Cómo se obtiene un conector que pueda soportar [that]? Nadie había hecho eso antes, [and so] tuvimos que inventar un material. Entonces tenemos doctorados en ciencia de materiales, [and] tuvimos que inventar un material que pudiera absorber algo de esa diferencia “.

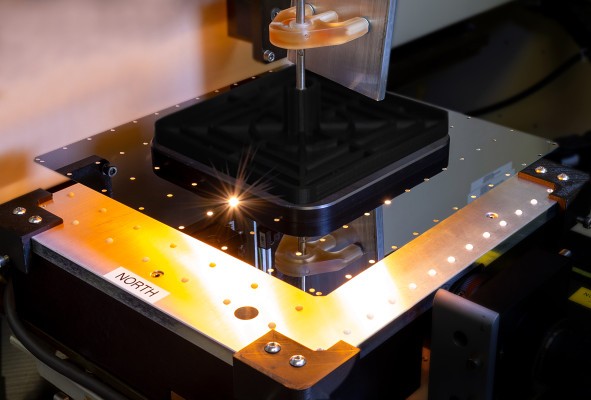

Una vez que se fabrica un chip, debe probarse y empaquetarse para su envío a los fabricantes de equipos originales (OEM) que agregan los chips a los productos utilizados por los clientes finales (ya sean centros de datos o computadoras portátiles de consumo). Sin embargo, existe un desafío: absolutamente nada en el mercado está diseñado para manejar un chip de oblea completa.

Cerebras diseñó su propio sistema de prueba y empaque para manejar su chip (Via Cerebras Systems)

“¿Cómo diablos lo empacas? Bueno, la respuesta es que inventas mucha mierda. Esa es la verdad. Nadie tenía una placa de circuito impreso de este tamaño. Nadie tenía conectores. Nadie tenía un plato frío. Nadie tenía herramientas. Nadie tenía herramientas para alinearlos. Nadie tenía herramientas para manejarlos. Nadie tenía ningún software para probar ”, explicó Feldman. “Y por eso hemos diseñado todo este flujo de fabricación, porque nadie lo ha hecho nunca”. La tecnología de Cerebras es mucho más que solo el chip que vende: también incluye toda la maquinaria asociada necesaria para fabricar y empaquetar esos chips.

Finalmente, toda esa potencia de procesamiento en un chip requiere una inmensa potencia y enfriamiento. El chip de Cerebras utiliza 15 kilovatios de potencia para operar, una cantidad prodigiosa de potencia para un chip individual, aunque relativamente comparable a un grupo de inteligencia artificial de tamaño moderno. Toda esa potencia también necesita ser enfriada, y Cerebras tuvo que diseñar una nueva forma de entregar ambos para un chip tan grande.

Básicamente abordó el problema girando el chip hacia un lado, en lo que Feldman llamó “usar la dimensión Z”. La idea era que, en lugar de tratar de mover la energía y enfriar horizontalmente a través del chip como es tradicional, se entregan energía y enfriamiento verticalmente en todos los puntos del chip, asegurando un acceso uniforme y consistente a ambos.

Y así, esos fueron los siguientes tres desafíos (expansión térmica, empaque y energía / enfriamiento) que la compañía ha trabajado las 24 horas para cumplir estos últimos años.

De la teoría a la realidad.

Cerebras tiene un chip de demostración (vi uno, y sí, es aproximadamente del tamaño de mi cabeza), y ha comenzado a entregar prototipos a los clientes según los informes. Sin embargo, el gran desafío, como ocurre con todos los chips nuevos, es aumentar la producción para satisfacer la demanda de los clientes.

Para Cerebras, la situación es un poco inusual. Dado que pone tanta potencia de cómputo en una oblea, los clientes no necesariamente necesitan comprar docenas o cientos de chips y unirlos para crear un clúster de cómputo. En cambio, es posible que solo necesiten un puñado de chips Cerebras para sus necesidades de aprendizaje profundo. La siguiente fase importante de la compañía es alcanzar la escala y garantizar una entrega constante de sus chips, que empaqueta como un “dispositivo” de todo el sistema que también incluye su tecnología patentada de enfriamiento.

Espere escuchar más detalles de la tecnología de Cerebras en los próximos meses, particularmente a medida que la lucha por el futuro de los flujos de trabajo de procesamiento de aprendizaje profundo continúa calentándose.